Parallel Input Serial Output Shift Register Verilog Code

Serial in serial out

At each clock cycle, the content of the register shifts to the right and sin enters into the leftmost bit or the MSB bit. The whole design also has and output that we are c calling sout. At each clock cyccle the right most bit of the register comes out. The picture shows the scheme of the shift register. Here is the verilog implemmentation of. The testbech for the Serial shift register Serial Input Serial Output Shift Register Exercizes 1. In test bench the shift register is instantiated with N=2. Verify that it behaves as expected. Repead the testbench and verification for N=4 2. Write the above code for left shift in place of right shift. The data now comes out of the MSB.

// File : Design of Serial In -

Serial Out Shift Register using d_flip

flop.v

module siso ( din ,clk ,reset ,dout );

output dout ;

input din ;

input clk ;

input reset ;

wire [2:0]s;

d_flip_flop u0 (.din(din),

.clk(clk),

.reset(reset),

.dout(s[0]));

d_flip_flop u1 (.din(s[0]),

.clk(clk),

.reset(reset),

.dout(s[1]));

d_flip_flop u2 (.din(s[1]),

.clk(clk),

.reset(reset),

.dout(s[2]));

d_flip_flop u3 (.din(s[2]),

.clk(clk),

.reset(reset),

.dout(dout));

endmodule

// -------------- D flip flop design -

-----------------------

//------------------------------

--------------------------------

---------------

//

// Title : d_flip_flop

// Design : upload_design1

// Author : Naresh Singh Dobal

// Company : nsd

//

//------------------------------

--------------------------------

---------------

//

// File : d_flip_flop.v

module d_flip_flop ( din ,clk ,reset

,dout );

output dout ;

reg dout;

input din ;

input clk ;

input reset ;

always @ (posedge clk)

begin

if (reset)

dout <= 1;

else

dout <= din;

end

endmodule

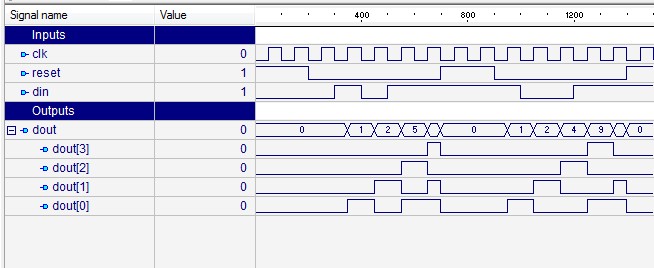

Serial in parallel out

// File : Serial IN Parallel OUT

Shift Register using Behavior

Modeling Style.v

module SIPO ( din ,clk ,reset ,dout );

output [3:0] dout ;

wire [3:0] dout ;

input din ;

wire din ;

input clk ;

wire clk ;

input reset ;

wire reset ;

reg [3:0]s;

always @ (posedge (clk)) begin

if (reset)

s <= 0;

else begin

s[3] <= din;

s[2] <= s[3];

s[1] <= s[2];

s[0] <= s[1];

end

end

assign dout = s;

endmodule

Parallel in parallel out

// File : parallel IN - Parallel

OUT Shift Register using Behavior

Modeling Style.v

module PIPO ( din ,clk ,reset ,dout );

output [3:0] dout ;

reg [3:0] dout ;

input [3:0] din ;

wire [3:0] din ;

input clk ;

wire clk ;

input reset ;

wire reset ;

always @ (posedge (clk)) begin

if (reset)

dout <= 0;

else

dout <= din;

end

endmodule

Parallel in serial out

// File : Parallel IN - Serial OUT

Shift Register.v

module parallel_in_serial_out ( din

,clk ,reset ,load ,dout );

output dout ;

reg dout ;

input [3:0] din ;

wire [3:0] din ;

input clk ;

wire clk ;

input reset ;

wire reset ;

input load ;

wire load ;

reg [3:0]temp;

always @ (posedge (clk)) begin

if (reset)

temp <= 1;

else if (load)

temp <= din;

else begin

dout <= temp[3];

temp <= {temp[2:0],1'b0};

end

end

endmodule

Ct4810 driver win7. 8-bit parallel-in/serial-out shift register

The 74LV165 is an 8-bit parallel-load or serial-in shift register with complementary serial outputs (Q7 and Q7) available from the last stage. When the parallel-load input (PL) is LOW, parallel data from the inputs D0 to D7 are loaded into the register asynchronously. When input PL is HIGH, data enters the register serially at the input DS. It shifts one place to the right (Q0→Q1→Q2, etc.) with each positive-going clock transition. This feature allows parallel-to-serial converter expansion by tying the output Q7 to the input DS of the succeeding stage.

4 Bit Shift Register Verilog

The clock input is a gate-OR structure which allows one input to be used as an active LOW clock enable input (CE) input. The pin assignment for the inputs CP and CE is arbitrary and can be reversed for layout convenience. The LOW-to-HIGH transition of the input CE should only take place while CP HIGH for predictable operation. Either the CP or the CE should be HIGH before the LOW-to-HIGH transition of PL to prevent shifting the data when PL is activated.

Features and benefits

- Wide supply voltage range from 1.0 V to 5.5 V

- Synchronous parallel-to-serial applications

- Optimized for low voltage applications: 1.0 V to 3.6 V

- Synchronous serial input for easy expansion

- Latch-up performance exceeds 250 mA

- 5.5 V tolerant inputs/outputs

- Direct interface with TTL levels (2.7 V to 3.6 V)

- Power-down mode

- Complies with JEDEC standards:

- JESD8-5 (2.3 V to 2.7 V)

- JESD8B/JESD36 (2.7 V to 3.6 V)

- JESD8-1A (4.5 V to 5.5 V)

- ESD protection:

- HBM JESD22-A114-A exceeds 2000 V

- MM JESD22-A115-A exceeds 200 V

- Specified from -40°C to +85°C and from -40°C to +125°C

Parametrics

| Type number | VCC (V) | Logic switching levels | Output drive capability (mA) | tpd (ns) | fmax (MHz) | No of bits | Tamb (°C) | Rth(j-c) (K/W) | |||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 74LV165D | Production | 1.0 - 5.5 | TTL | ± 12 | 18 | 78 | 8 | low | -40~125 | 91 | 9.3 | 51 | SO16 |

| 74LV165DB NRND | Not for design in | SSOP16 | |||||||||||

| 74LV165PW | Production | 1.0 - 5.5 | TTL | ± 12 | 18 | 78 | 8 | low | -40~125 | 120 | 3.3 | 48.7 | TSSOP16 |

Package

| Package | Package information | Reflow-/Wave soldering | Status | ||||

|---|---|---|---|---|---|---|---|

| 74LV165D | SO16 (SOT109-1) | SOT109-1 | SO-SOJ-REFLOW SO-SOJ-WAVE | Reel 13' Q1/T1 | Active | 74LV165D | 74LV165D,118 (9351 560 60118) |

| Bulk Pack | Active | 74LV165D | 74LV165D,112 (9351 560 60112) | ||||

| 74LV165DB NRND | SSOP16 (SOT338-1) | SOT338-1 | SSOP-TSSOP-VSO-REFLOW SSOP-TSSOP-VSO-WAVE | Reel 13' Q1/T1 | Active | LV165 | 74LV165DB,118 (9351 660 30118) |

| Bulk Pack | Active | LV165 | 74LV165DB,112 (9351 660 30112) | ||||

| 74LV165PW | TSSOP16 (SOT403-1) | SOT403-1 | SSOP-TSSOP-VSO-WAVE | Reel 13' Q1/T1 | Active | LV165 | 74LV165PW,118 (9351 745 40118) |

| Bulk Pack | Active | LV165 | 74LV165PW,112 (9351 745 40112) |

Quality, reliability & chemical content

| Leadfree conversion date | ||||||||

|---|---|---|---|---|---|---|---|---|

| 74LV165D | 74LV165D,118 | 74LV165D | week 6, 2004 | 144.9 | 10.23 | 9.78E7 | 1 | 1 |

| 74LV165D | 74LV165D,112 | 74LV165D | week 6, 2004 | 144.9 | 10.23 | 9.78E7 | 1 | 1 |

| 74LV165DB NRND | 74LV165DB,118 | 74LV165DB | week 12, 2005 | 1 | 1 | |||

| 74LV165DB NRND | 74LV165DB,112 | 74LV165DB | week 12, 2005 | 1 | 1 | |||

| 74LV165PW | 74LV165PW,118 | 74LV165PW | week 17, 2005 | 144.9 | 10.23 | 9.78E7 | 1 | 1 |

| 74LV165PW | 74LV165PW,112 | 74LV165PW | week 17, 2005 | 144.9 | 10.23 | 9.78E7 | 1 | 1 |

Quality and reliability disclaimer

Quality and reliability disclaimerDocumentation (10)

| File name | Title | Type | Date |

|---|---|---|---|

| 74LV165 | 8-bit parallel-in/serial-out shift register | Data sheet | 2017-03-17 |

| Nexperia_Selection_guide_2020 | Nexperia Selection Guide 2020 | Selection guide | 2020-01-31 |

| SO-SOJ-REFLOW | Footprint for reflow soldering | Reflow soldering | 2009-10-08 |

| SO-SOJ-WAVE | Footprint for wave soldering | Wave soldering | 2009-10-08 |

| SOT109-1 | plastic, small outline package; 16 leads; 1.27 mm pitch; 9.9 mm x 3.9 mm x 1.35 mm body | Package information | 2020-04-21 |

| SSOP-TSSOP-VSO-WAVE | Footprint for wave soldering | Wave soldering | 2009-10-08 |

| SOT403-1 | plastic, thin shrink small outline package; 16 leads; 5 mm x 4.4 mm x 1.1 mm body | Package information | 2020-04-21 |

| SSOP-TSSOP-VSO-REFLOW | Footprint for reflow soldering | Reflow soldering | 2009-10-08 |

| SSOP-TSSOP-VSO-WAVE | Footprint for wave soldering | Wave soldering | 2009-10-08 |

| SOT338-1 | plastic, shrink small outline package; 16 leads; 0.65 mm pitch; 6.2 mm x 5.3 mm x 2 mm body | Package information | 2020-04-21 |

Support

If you are in need of design/technical support, let us know and fill in the answer form, we'll get back to you shortly.

Shift Left Register Verilog

Ordering, pricing & availability

Sample

As a Nexperia customer you can order samples via our sales organization or directly via our Online Sample Store: https://extranet.nexperia.com.

Bidirectional Shift Register Verilog Code

Sample orders normally take 2-4 days for delivery.

Shift In Verilog

If you do not have a direct account with Nexperia our network of global and regional distributors is available and equipped to support you with Nexperia samples.